高分辨率並行接口線陣CCD

• CCD芯片:東芝TCD1304DG,像素大小為 8um×200um,像素共3648,波長響應範圍為300nm~1100nm。

• AD採樣速率:187.5kHz。

• AD採樣深度:13Bit。

• CCD驅動及數據採樣控制電路由Cyclone fpga完成。

• CCD的積分曝光時間999級可調,最大積分時間為20ms,最小積分時間為20us。

• 通信接口採用8Bit並行數據接口(D0~D7),配合片選

(Chip-En),讀寫控制(R/W)和時鐘信號(Clk)等完成外部控制電路對CCD的讀寫控制。

• 讀寫控制時鐘信號Clk由外部控制電路提供,在寫信號時,時鐘頻率最高不要超過50MHz,最低沒有限制;讀數據時,時鐘頻率最高不要超過50MHz,最低沒有限制,因為內部CCD的控制板內含有緩存,外部控制電路讀取數據的速度再低,也不會造成CCD像素數據丟失。

• 讀在上面主圖片的左下角還有其它圖片的圖標,用戶可以查看其寫入和讀出數據控制信號的時序。用戶若需了解更多信息,請聯繫索要說明書。

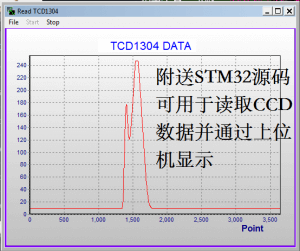

• 附送利用arm STM32F103控制讀取此CCD數據並通過上位機軟件顯示的例程和源碼,例程包含內容有:設置ccd積分時間;讀取CCD數據並處理;上位機軟件顯示ccd像素數據。

瀏覽人數: 667